## E-band Frequency Sextupler with >35dB Harmonics Rejection over 20GHz Bandwidth in 55nm BiCMOS

Mahmoud M. Pirbazari, member, IEEE, Andrea Mazzanti, Senior Member, IEEE

Abstract— A frequency multiplier by 6 (sextupler) for LO generation in E-band is presented. It comprises a tripler, a doubler, and an output buffer. A detailed analysis is proposed to discuss the optimal order of the multiplication stages to minimize unwanted harmonics of the input. Moreover, novel circuit topologies for the tripler and doubler are introduced. The tripler core is devised to reproduce the trans-characteristic of a 3rd order polynomial that ideally generates only the 3<sup>rd</sup> harmonic of a sinusoidal input signal. By leveraging an envelope detector for adaptive biasing, the circuit maintains excellent suppression of the driving signal and unwanted harmonics over wide variations of the input power. The proposed topology improves output signal purity and current conversion efficiency against classical triplers based on transistors biased in class C. The cascaded frequency doubler is based on a novel push-push configuration that provides a differential output and excellent odd-order harmonic rejection thanks to an enhanced robustness to amplitude and phase unbalances of the driving signal. The sextupler is fabricated in a 55nm SiGe-BiCMOS technology. Driven with a 0dBm input signal and consuming 63.1mW of DC power, it delivers Pout up to 5.6dBm at 72GHz. Pout is above 0dBm over 20GHz bandwidth while undesired harmonics of the input are suppressed by more than 35dB. Compared to previously reported millimeter-wave frequency multipliers, the sextupler demonstrates improved harmonic rejection, conversion gain and efficiency, without compromising the operation bandwidth and output power.

*Index Terms*—Frequency multiplier, sextupler, tripler, doubler, LO generation, BiCMOS, millimeter-waves.

#### I. INTRODUCTION

C ommunications at millimeter waves (mm-waves) are rapidly gaining interest due to the wide available bandwidth which translates into higher data transmission capacity [1]. Generation of the transceivers local oscillation (LO) is critical because many contrasting requirements, i.e. tuning range (TR), phase noise (PN), output power, and level of spurious tones, affect the system performance. Differently from what is commonly pursued at radio frequency, LO generation with a phase locked loop (PLL) embedding a voltage-controlled oscillator (VCO) at the desired output frequency is not viable at mm-waves. In fact, the severe impact of device parasitics and the low quality factor of passive components in silicon (mostly variable capacitors) impair the achievable PN and TR. At mmwaves, designs in CMOS technology have reported around 10% of TR [2-4], while bipolar transistor technologies enable larger TR [5, 6], up to 28% in [7] using a BiCMOS process. However, in any case, digital frequency dividers in the PLL running at mm-waves need excessive power consumption.

A commonly pursued approach consists of a PLL in the 10-20GHz range, where silicon VCOs feature the best figure of merit, followed by a frequency multiplier. However, the multiplier must provide good suppression of the driving signal and undesired harmonics not to impair the transceiver performance, particularly with high-order, spectrally efficient modulation schemes [8].

LO generation at mm-waves or sub-THz range with a source at 10-20GHz requires a high multiplication factor. Subharmonic injection locked oscillators (S-ILO) suffer from narrow bandwidth due to the limited locking range (LR). In [9], a S-ILO multiplier by 13 to 15 with 12% fractional bandwidth output frequency was demonstrated implementing a frequency tracking loop for tuning the locked oscillator at 30GHz. The operation bandwidth is therefore limited by the frequency tuning range of the oscillator which is significantly penalized if the operation frequency is increased. N-push technique [10, 11], mixing [12-14], and edge combining [15] are other methods that can potentially allow high multiplication factors. They all rely on manipulation of equally spaced phase-shifted signals, with the accuracy of the phase shifts being crucial to achieve high spur rejection. The high output power and high spur rejection in [10] was achieved at the cost of a very small operation bandwidth (1.4%) and high power consumption of the multi-phase ring oscillator. The tripler architecture in [7], very well suited for advanced CMOS nodes, would be much less power efficient if implemented in a pure bipolar or BiCMOS technology. In addition, higher multiplication factor needs increasing the number of phases and if they are generated by a ring oscillator, increasing the number of stages reduces the oscillation frequency

A more robust approach is by cascading multiplication stages, of smaller factors, where harmonics of the input signal are generated by transistors biased in class B/C. Following this approach, a sextupler was proposed in [16], multipliers by nine in [17] and [18], and octuplers in [19] and [20], with respective rejection of unwanted harmonics of 25, 31, 37, 40 and 20 dB. Despite the medium to high achieved bandwidth in these works, the use of low-efficiency harmonic generation circuits and the need for several filtering stages to reach acceptable rejection of

Manuscript received Month Day, Year; revised Month Day, Year; accepted Month Day, Year. Date of publication Month Day, Year; date of current version Month Day, Year. (Corresponding author: Mahmoud M. Pirbazari).

This work was conducted within the framework of the H2020 DRAGON project (www.h2020-dragon.eu/), funded by the Commission of the European Union (Grant Agreement No. 955699).

The authors are with the department of electrical, computer and biomedical engineering, University of Pavia, Pavia, Italy (e-mail: <u>mahmoud.pirbazari</u> <u>@unipv.it</u>).

Digital Object Indentifier xx.yyyy/JJJJJ.2020.zzzzzz.

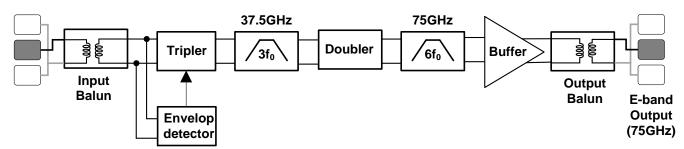

Fig. 1. Block diagram of the frequency multiplier by 6 (sextupler).

unwanted harmonics led to excessive power consumption, above 400mW, or very low output power. Combining class-C transistors with the high gain and high selectivity of ILO buffers improves the rejection of unwanted harmonics at low power consumption, as proved by the sextupler in [21] or the quadrupler in [22], but at the cost of respectively 1.5% and 6.9% fractional bandwidth only. Finally, mixing and injection locking techniques were used together in more sophisticated designs to cover a larger frequency range. In [23] the multiplication factor can be varied by programming switchable inductors, hence changing the number of harmonic to be locked on. However, application of the technique to higher frequency is challenging as inductors size shrink. Also in [24] and [25] different multiplication factors are available, but at different output taps, limiting its usage.

Comparison of the different methods to implement frequency multipliers with high multiplication factors reveals that cascaded stages excel at simplicity and robustness, hence they are preferrable at mm-waves frequency. On the other hand, the generation of several undesired harmonic components by transistors in class B/C sets a severe trade-off between the level of harmonics, operation bandwidth and power consumption. Meanwhile, sensitivities to transistor bias point or input power level appear as challenges to these otherwise robust circuits.

In this work, a frequency sextupler for LO generation at Eband with high harmonics rejection, wide bandwidth and low power consumption is proposed. Choice of the LO multiplication factor is driven by several aspects which includes location of spurious tones, availability or feasibility of the PLL, distribution of the signal and optimization of the overall power efficiency. The proposed sextupler is designed within the framework of the European project DRAGON, aimed at developing an high-capacity transceivers for backhaul in 5G and beyond [26], which makes use of a low phase noise commercial synthesizer in X band and needs generation of a signal in E-band. The block diagram of the sextupler is shown in Fig. 1. It is composed of a novel frequency tripler and doubler. The proposed tripler substantially improves the rejection of unwanted harmonics against class-C multipliers without relying on complex filtering stages [27]. A novel topology for the frequency doubler is also introduced. Compared to the widespread push-push doublers [28-30] the presented solution provides a differential output and excellent odd-order harmonic rejection thanks to an enhanced robustness to amplitude and phase unbalances of the driving signal. The

sextupler is realized in a 55nm SiGe-BiCMOS technology. A test chip consumes 63.1mW of DC power of which 39.1mW is consumed by the output buffer. The maximum output power is 5.6 dBm and remains above 0dBm from 64.7 GHz to 84.7 GHz, while all undesired harmonics are suppressed by at least 35 dB.

The rest of the paper is organized as follows: Sec-II analyzes the challenges of the most widely adopted solutions for harmonic generation in mm-waves frequency multipliers. Sec-III describes the proposed sextupler architecture with a discussion about the most convenient ordering of multiplier stages to minimize the level of unwanted harmonics. The proposed tripler is introduced in Sec. IV while the doubler and output buffer are presented in Sec-V. Measurements are reported in Sec. VI where the results are also compared with previously reported mm-waves frequency multipliers. Sec. VII concludes the paper.

# II. FREQUENCY MULTIPLICATION WITH CLASS-B/C TRANSISTORS

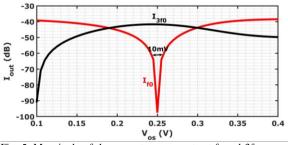

The most common approach for frequency multiplication is by generating harmonics of a driving signal with a transistor biased in class-B/C, as shown in Fig. 2a, and selecting the desired harmonic with a frequency selective load impedance. For frequency multiplication by N, the LC load is tuned to a center frequency of  $Nf_0$  (being  $f_0$  the input signal frequency). The -3dB bandwidth (BW) is inversely proportional to the filter quality factor:  $BW = Nf_0/Q$ . The harmonic content of the transistor current, Iout, is set by the transistor conduction angle,  $\theta$ , determined by the bias voltage V<sub>bias</sub>. To gain insight, the top plot in Fig. 2b reports the simulated short-circuit collector currents at fundamental frequency,  $2^{nd}$ , and  $3^{rd}$  harmonic (I<sub>f0</sub>, I<sub>2f0</sub>, I<sub>3f0</sub> respectively), normalized to transistor area, as a function of the estimated  $\theta$ . The harmonic rejection ratio (HRR), defined as the ratio between the power of the desired signal and the power of unwanted harmonics, is limited by  $I_{f0}$ , i.e. the leakage of the driving signal, which is always larger than I<sub>2f0,3f0</sub>, as evident also from the bottom plot in Fig. 2b, showing the ratio  $I_{f0}/I_{2f0}$  and  $I_{f0}/I_{3f0}$ . The optimum conduction angle for the desired harmonic can be selected based on the required HRR and output power. As an example, in case of a tripler,  $\theta \approx 140^{\circ}$ maximizes  $I_{3f0}$  and hence the tripler output amplitude but  $I_{f0}$  is 10dB larger than I<sub>3f0</sub> (bottom plot). Targeting a bandwidth of 15% (Q=6.7) the rejection of  $I_{f0}$  from the LC load is  $20\log(3)+20\log(Q)=26dB$ , leading to HRR=26-10=16dB only on the tripler output voltage (Vout). Looking at the plots in Fig.

Fig. 2. (a) Single BJT biased in class-B/C as a harmonic generator, (b) Harmonics of  $I_{out}$ , (c) Differential version for odd-order multipliers, (d) Differential version for even-order multipliers (push-push).

2b,  $I_{f0}/I_{3f0}$  is minimized (from 10dB to 4dB) at low  $\theta$ . This improves HRR by 6dB, from 16dB to 22dB. However,  $I_{3f0}$  at  $\theta \approx 80^\circ$  is roughly 7 times lower than at  $\theta \approx 140^\circ$ . Therefore, the mild improvement of HRR comes at the price of 17dB output amplitude reduction. A similar conclusion can be drawn for the case of a doubler. That is, HRR can be mildly improved at the price of significant reduction of the desired tone's amplitude. In addition, limited current conversion efficiency,  $\eta_C = I_{Nf0}/I_{DC}$ , (being N the number of the desired harmonic) is another limitation of harmonic generation with class-B/C transistors. Looking at the curves in Fig. 2b and considering the case of a tripler, we can see that  $\eta_C$  is at most 0.5 at the angle of maximum  $I_{3f0}$ .

In summary, despite its simplicity, the class-B/C multiplier suffers from poor suppression of the driving signal and efficiency. As shown in Fig. 2c and Fig. 2d, the performance of class-B/C harmonic generators can be improved to realize multipliers by odd or even factor respectively. In a differential topology (Fig. 2c) the odd harmonics of the input signal in I<sub>A</sub> and I<sub>B</sub> are in opposite phase, following  $V_{in}^{\pm}$ , whereas the even harmonics are in phase. Therefore, the even harmonics of the input are ideally canceled on the differential output. Nevertheless, the strong leakage of the driving signal is not cancelled. Frequency triplers based on topologies depicted in Fig. 2a and Fig.2c are widely reported in the literature. The HRR, dominated by leakage of the driving signal, is typically in the 20-30dB range [31-35]. The suppression of the driving signal could be improved by rising the filter selectivity at the cost of larger power consumption or bandwidth limitation [36].

The circuit topology in Fig.2d, (commonly named pushpush) is employed in frequency doublers. The anti-phase odd harmonics of the differential input signal cancel each other while the even harmonics add constructively. Ideally, there should be no fundamental component introduced by a balanced doubler. However, the fundamental tone is always present due to device mismatches, amplitude and phase unbalances in the input signals and capacitive coupling. As a matter of fact, the leakage of the driving signal remains the dominant spurious tone, still limiting the HRR to 20-30dB. Many works have demonstrated use of the push-push stage [28-30, 37, 38] or alternative topologies [39] at various frequencies and achieved wide bandwidth with around 20dB suppression of the driving signal. In [40] the leakage of the fundamental has been associated in part with the imbalances of the input balun, hence with a careful design focused to improve symmetry of the balun, 30dB suppression of the  $f_0$  was achieved.

#### III. FREQUENCY SEXTUPLER ARCHITECTURE

The proposed frequency sextupler, already introduced in Fig. 1, is composed of a tripler, a doubler, and an output buffer. When frequency multipliers are cascaded, intermodulation of each stage folds the harmonics generated by the previous stage and creates new harmonic tones at the output. As an example, if a tripler precedes a doubler, the component at  $f_0$  leaked to the tripler output can get mixed with the main component at  $3f_0$  and generate a tone at  $4f_0$  at the doubler output. This issue is critical as tones generated by intermodulation can be very close to the desired signal and finally difficult to be filtered out. Therefore, an important aspect to be considered is the order of the multiplication stages that keeps the spurious tones from intermodulation low and as far as possible from the main tone. In case of a frequency sextupler, there are two options: *Tripler first* and *Doubler first*.

As discussed in the previous section, the largest undesired output tone in both doublers and triplers is the leakage of the driving signal. Therefore, assuming a sinusoidal input,  $x(t) = A \cos(2\pi f_0 t)$ , the operation of a frequency doubler can be approximated by the following polynomial:

$$y(t) = \frac{1}{A\rho} x(t) + \frac{2}{A^2} x(t)^2$$

(1)

where  $\rho$  accounts for the finite doubler suppression of the tone at f<sub>0</sub> with respect to 2f<sub>0</sub> i.e.  $\rho = y_{2f_0}/y_{f_0}(y_{2f_0}, y_{f_0})$  are the fundamental and second harmonic of y) Similarly, the tripler operation can be approximated by the following polynomial:

$$w(t) = \frac{1-3\gamma}{A\gamma} x(t) + \frac{4}{A^3} x(t)^3$$

(2)

where  $\gamma$  accounts for the tripler suppression of the tone at  $f_0$ with respect to  $3f_0$  i.e.  $\gamma = w_{3f_0}/w_{f_0}$  ( $w_{3f_0}, w_{f_0}$  are the fundamental and third harmonic of w) Modeling the doubler and the tripler with (2) and (3), the two options for implementing a sextupler can now be compared.

#### A. Doubler First:

When the doubler is the first block in the chain, using (1) and omitting the generated DC component, the output is:

$$y(t) = \frac{1}{\rho} \cos(\omega_0 t) + \cos(2\omega_0 t)$$

(3)

The doubler output is then fed to the tripler. By substituting (3) in (2) and keeping only the tones closest to the desired one  $(6\omega_0 t)$ , the sextupler output is approximated by:

$$w(t) \approx \frac{3}{\rho^2} \cos(4\omega_0 t) + \frac{3}{\rho} \cos(5\omega_0 t) + \cos(6\omega_0 t) \tag{4}$$

As the 5<sup>th</sup> harmonic is the closest tone to the desired  $6\omega_0$  signal (thus it is the most difficult to filter out) we focus our attention to it. Assuming  $\rho = 30$ , which corresponds to 29.5dB of driving signal suppression of the doubler alone, consistent with the results in the literature [33-35], from (4) the 5<sup>th</sup> harmonic is only 20dB below the desired signal.

### B. Tripler first:

Following the same approach as in the previous case, using (2) the output of a tripler excited by a single tone at  $\omega_0$  can be approximated by

$$y(t) = \frac{1}{2}\cos(\omega_0 t) + \cos(3\omega_0 t) \tag{5}$$

The tripler output is then fed to a doubler. In this case, the doubler output is obtained by substituting (5) in (1). Keeping only the tones closest to  $6\omega_0$ , the output is:

$$w(t) \approx \frac{2}{\gamma} \cos(4\omega_0 t) + 0 \times \cos(5\omega_0 t) + \cos(6\omega_0 t)$$

(6)

Comparing (6) and (4) leads us to an important result: in the case of *tripler first*, the 5<sup>th</sup> harmonic ideally disappears. This is a key difference because, due to the small spectral distance to the desired tone, filtering the 5<sup>th</sup> harmonic is challenging.

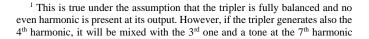

In the above analysis, made by approximating the two multipliers with (1) and (2), only the finite suppression of the driving signal frequency has been considered. A more accurate analysis can be done by considering more terms in the polynomials responsible for leakage also of the 4<sup>th</sup> harmonic in the doubler and 5<sup>th</sup> harmonic in the tripler. The 4<sup>th</sup> and 5<sup>th</sup> harmonics are assumed 10dB lower than the leakage of the fundamental, a realistic scenario assuming that the two circuits are cascaded with mild interstage filtering. Fig. 3 shows a graphical representation of the results assuming  $\rho = \gamma = 30$ . The  $4^{\text{th}}$  and  $8^{\text{th}}$  harmonics at the output of the sextupler ( $4f_0$ ,  $8f_0$ ) are almost equally suppressed in both cases. However, the tripler first chain (Fig. 3b) provides 48dB more suppression of the 5<sup>th</sup> harmonic and the 7<sup>th</sup> harmonic ideally disappears completely<sup>1</sup>. The more accurate analysis confirms that placing the tripler before the doubler is still preferrable to limit the level of undesired harmonics at the output.

Fig. 3. Effect of multipliers' order on output spurs. (a) *Doubler first*, (b) *Tripler first*.

Another important observation that can be made with the above analysis is the influence of harmonic rejection levels of the first and second block in the chain on the overall harmonic rejection. By assigning different values to  $\gamma$  and  $\rho$  in the two cases considered, it is observed that the first block plays always a more dominant role. As an example, in the case of *tripler first*,  $\gamma = 20$  and  $\rho = 40$  results in 19.6 dB and 29 dB suppression of the 4<sup>th</sup> and 8<sup>th</sup> harmonics, respectively, whereas  $\gamma = 40$  and  $\rho = 20$  results in 25.6 dB and 34.5dB suppressions. Therefore, it can be concluded that particular care must be paid on the harmonic suppression performance of the first stage to maintain low level of unwanted harmonics at the output of the chain.

#### IV. FREQUENCY TRIPLER

#### A. Principle of operation

Assuming a sinusoidal driving voltage,  $V_{in}(t)=Asin(2\pi f_0 t)$ , the active core of an ideal tripler that generates current only at the 3<sup>rd</sup> harmonic must display a trans-characteristic which follows the 3<sup>rd</sup> order polynomial<sup>2</sup>:

$$I_{out} = \left(\frac{3}{A}v_{in} - \frac{4}{A^3}v_{in}^3\right)g_m \tag{7}$$

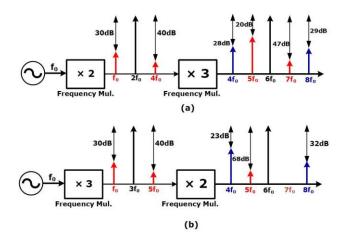

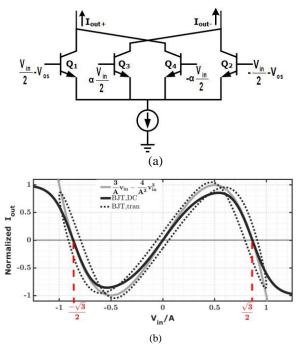

Fig. 4a shows the proposed circuit schematic to approximate (7) while the ideal and transistors trans-characteristics are plotted in Fig. 4b.

Looking at the circuit schematic,  $Q_{3,4}$  are driven by the input signal attenuated by  $\alpha$  while  $Q_{1,2}$  are directly driven by the input signal but with a negative DC level shift (-V<sub>os</sub>) with respect to the base of  $Q_{3,4}$ . The circuit operation is as follows: at small V<sub>in</sub>, the lower bias voltage keeps  $Q_{1,2}$  off and the circuit approximates (7) near the origin with a simple differential pair formed by  $Q_{3,4}$ . But when V<sub>in</sub> rises,  $Q_{1,2}$  turn on, subtract current from the outputs and reverse the slope of the transcharacteristic. Notably, at each half cycle almost all the tail current is steered to one branch and then to the other, creating a

will be generated at the doubler output. Therefore, this tone normally does not totally vanish in practical cases.

<sup>&</sup>lt;sup>2</sup> The presence of A in Eq.(7) means that the trans-characteristic has to be adapted to the amplitude of the input signal.

Fig. 4. (a) Simplified schematics of the proposed tripler core (b) comparison of the trans-characteristic with Eq. (7).

$3^{rd}$  harmonic current at the output with an amplitude close to that of the tail DC current. This implies a current conversion efficiency close to one. Looking at the upper plot in Fig. 2b, in a multiplier based on the non-linearity of a transistor biased in class-C, the magnitude of  $I_{3f0}$  is close to half of  $I_{DC}$  at maximum  $I_{3f0}$ , implying a current conversion efficiency roughly half of the proposed circuit.

The zero crossings of the current offsetted from the origin in the trans-characteristic of Fig. 4b occur when the voltage at the base of Q<sub>3,4</sub> equals the voltage at the base of Q<sub>1,2</sub> i.e.  $\frac{1}{2}\alpha V_{in} = \frac{1}{2}V_{in} - V_{os}$ . This condition is satisfied for  $V_{in} = \pm 2 V_{os}/(1 - \alpha)$ . The zero crossings of (7) are at  $V_{in} = \pm \sqrt{3}A/2$ . Therefore,  $V_{os}$  and  $\alpha$  must be selected to satisfy:

$$\frac{2V_{os}}{(1-\alpha)} = \frac{\sqrt{3}}{2}A\tag{8}$$

Further circuit analysis proves that setting  $\alpha$ =0.2 allows to fit the slope of (7) near the three zero crossings. With  $\alpha$  fixed, (8) shows that to maintain the correct zero crossings at different input power, V<sub>os</sub> must be varied linearly with the input signal amplitude (A). Therefore, V<sub>os</sub> is generated by an envelope detector, shown in the block diagram of Fig. 1.

In Fig. 4b the black solid line shows the DC transcharacteristic of the BJT implementation, well approximating the ideal curve in gray. Simulations at low frequency confirm that the circuit suppresses almost completely the component at  $f_0$  in the output current. With a driving signal at 12.5GHz, device parasitic capacitors distort the dynamic shape of the trans-characteristic and reduce the  $f_0$  suppression, but the issue can be solved by resonating out the equivalent shunt capacitance at the common-emitter node at frequency  $2f_0$ . To gain insight on the achievable  $f_0$  rejection, simulated tripler output current is plotted versus  $V_{os}$  in Fig. 5. It can be observed

Fig. 5. Magnitude of the current components at  $f_0$  and  $3f_0$  versus  $V_{os}$ , derived from simulation with 12.5GHz input signal.

that the rejection is ultimately bounded by the accuracy to which  $V_{os}$  is set. At the optimal  $V_{os}$  the rejection is greater than 50dB, but remains above 20dB if  $V_{os}$  is set with +/-5mV accuracy.

Looking again at Fig. 4b, the dotted curve is obtained by plotting  $I_{out}(t)$  against  $V_{in}(t)$  from transient simulations at 12.5GHz input frequency of the implemented circuit, detailed in the next sub-section. The curve shows that the transistor implementation approximates well the ideal behavior also at high frequency.

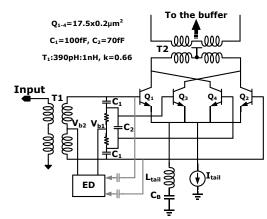

#### B. Tripler Circuit Design

The complete tripler circuit is shows in Fig. 6. The differential signal provided by the transformer balun, T1, directly drives the base of  $Q_{1,2}$  while it is attenuated by  $\alpha$  through a capacitive voltage divider ( $C_1$ ,  $C_2$ ) to feed the base of  $Q_{3,4}$ . The four transistors have the same emitter area. The inductor  $L_{tail}$  resonates with the equivalent shunt capacitance at the common-emitter node and  $C_B$  is sized sufficiently large to act as an AC short. The quality factor of  $L_{tail}$  is not critical, because the impedance at resonance is limited by the equivalent resistance at the emitters of  $Q_{1-4}$ . The transformer  $T_2$  provides the supply voltage and couples the tripler to the cascaded circuits. The transformer network is tuned to achieve a fractional bandwidth of 16%, centered at 37.5GHz.

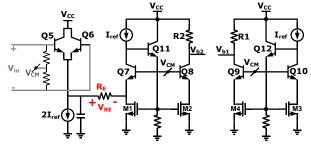

$V_{b2}$  and  $V_{b1}$  are the bias voltages for  $Q_{1,2}$  and  $Q_{3,4}$ respectively. They are generated by the envelope detector (ED) block such that  $V_{b1}$ - $V_{b2}$  (corresponding to  $V_{os}$  in Fig. 4) tracks the amplitude of the driving signal. The ED circuit schematic is shown in Fig. 7. Q<sub>5-10</sub> share the same base bias voltage,  $V_{CM} \approx 1.2$ , generated by a resistor string. In this way,  $Q_{5,6}$  (driven by  $V_{in}(t)$  and Q<sub>7</sub>, set V<sub>RE</sub> equal to the average value of  $/V_{in}(t)/$ . If  $V_{in}(t) = A \sin(2\pi f_0 t)$ ,  $V_{RE} = A/\pi$  and  $I_{RE} = (A/\pi)/R_E$ . M<sub>1,2</sub> mirror  $I_{ref}+I_{RE}$  into  $R_2$  while  $M_{3,4}$  mirror  $I_{ref}$  into  $R_1$  leading to  $V_{b2}=V_{cc}$ - $(I_{ref}+I_{RE})R_2, V_{b1}=V_{cc}-I_{ref}R_1$ . Assuming  $R_1=R_2$  results in  $V_{os}=V_{b1}$ - $V_{b2} = R_2 I_{RE} = (A/\pi)(R_2/R_E)$ . The ratio  $R_2/R_E$  is selected such that  $V_{os}$  satisfies (8) with  $\alpha$ =0.2, thus allowing to maintain good suppression of the fundamental frequency component independently from the amplitude of the input signal. All BJTs in Fig. 6 have an emitter area of  $0.45 \times 0.2 \mu m^2$ , and  $R_2$  and  $R_E$ are  $4.5k\Omega$  and  $5.8k\Omega$ , respectively. The total current consumption of the envelop detector is 600µA.

A first tripler chip has been realized [27] where a linear and wideband buffer, designed with the purpose of performing accurate experimental characterization, follows the tripler. The

Fig. 6. Detailed schematics of the proposed tripler.

Fig. 7. Envelope detector circuit for adaptive biasing of the tripler core.

buffer is a resistively degenerated cascode differential pair with resistive load and peaking inductors. From simulations, it introduces 9.6dB voltage attenuation with flat bandwidth up 70GHz, allowing measurements up to the 5<sup>th</sup> harmonic of the input. The output power at 1dB gain compression point is 1dBm.

#### C. Tripler measurement results

The frequency tripler has been implemented in ST Microelectronics 55nm SiGe-BiCMOS technology. The onchip buffer provides a differential output, but measurements are performed single-ended by probing each of the two outputs separately. Fig. 8 shows the measured power delivered to a  $50\Omega$ load at  $3f_0$  and the leakage of  $f_0$  and  $5f_0$  versus frequency when the tripler is driven by a 0dBm input signal. The single-ended peak output power is 0dBm at 37.8GHz and remains within -3dB variation from 35 GHz to 41GHz, corresponding to 15.8% fractional bandwidth. In this frequency range, minimum and maximum rejection of fo are 39dB and 43.8dB. Minimum and maximum rejection of 5f<sub>0</sub> are 37.5dB and 45.3dB, respectively. The tripler and ED draw 13.6mA from a 1.7V supply. The output buffer, not optimized for power efficiency but for wide bandwidth, high linearity and good common-mode rejection, draws 32mA from a 3V supply.

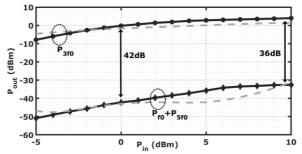

Fig. 9 shows the measured output power at  $3f_0$  when the input power is swept at 12.5GHz. The same plot reports the total HRR considering up to  $5f_0$ . In the input power range -5dBm to 10dBm the single-ended output power at  $3f_0$  rises from -8dBmto +4dBm. The HRR is better than 40dB until 4dBm input power and decreases to 36.6dB for 10dBm input power.

Fig. 8. Measured (solid) and simulated (dashed) tripler output power at the  $3^{rd}$  harmonic, fundamental, and the  $5^{th}$  harmonic versus frequency with 0dBm input signal. Chip photo is reported as inset [27].

Fig. 9. Measured (solid) and simulated (dashed) output power of the tripler showing  $3^{rd}$  harmonic and HRR versus input power at  $f_0=12.5$ GHz.

In summary, measurement results confirms the excellent rejection of undesired harmonics by the proposed tripler and robust operation over wide interval of input signal power.

#### V. FREQUENCY DOUBLER

Conventional frequency doublers are based on the push-push circuit configuration introduced in Sec. II, due to its simplicity and robustness. Considering the schematic drawn in Fig. 10a, where the bias current is set by Itail and a large capacitor sets AC ground to the common-emitter node, provided the driving signals  $V_{in}^{\pm}$  are perfectly differential, the input signal frequency and odd harmonics are intrinsically suppressed on the output current, Iout. However, if the inputs are not perfectly balanced, i.e. in the presence of amplitude mismatch and phase deviation from 180°, the common-mode component, at the fundamental frequency, is transferred to the output and amplified. This is the main issue limiting the rejection of the driving signal frequency component in the simple push-push doubler [28-30]. Moreover, the circuit topology in Fig. 10a generates a single-ended output, while a differential signal is often desirable in integrated transceivers. A balun transformer (e.g. coupled inductors [41, 42]) cascaded to the push-push pair can provide single-ended to differential conversion, but the interwinding parasitic capacitance impairs the amplitude and phase matching, particularly at mm-waves [43, 44].

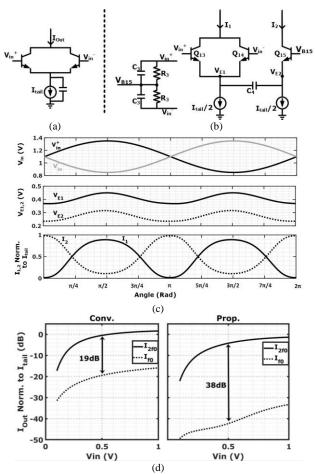

The core of the proposed frequency doubler, shown in Fig. 10b, is based on a push-push transistor pair but produces a differential output current and it features enhanced robustness against amplitude and phase unbalance of the driving signals, thus improving substantially the rejection of the fundamental frequency component. The differential input signals  $V_{in}^{\pm}$  drive the base of the push-push transistors Q<sub>13,14</sub> while the common-

Fig. 10. (a) Schematics of a simple push-push doubler and (b) of the proposed doubler. (c) Time-domain waveforms. (d) Leakage of the fundamental component assuming 0.5dB amplitude and  $5^{\circ}$  phase imbalance on the driving signals.

mode voltage, extracted through the RC network in Fig. 10b, feeds the base of  $Q_{15}$ . As in the simple push-push doubler of Fig. 10a, the currents through  $Q_{13}$  and  $Q_{14}$  are composed of outof-phase fundamental components (and odd-order harmonics) which cancel each other out, and in-phase  $2^{nd}$  harmonic components which add constructively to generate  $I_1$  with a fundamental at twice the input frequency. The right branch of the circuit, with  $Q_{15}$  in common base, provides the differential output and enhances the robustness to amplitude and phase errors in  $V_{in}^{\pm}$ .

Assuming C<sub>4</sub> (400fF) is large enough to be a short circuit at the operation frequency, the emitter current of Q<sub>13,14</sub>, I<sub>1</sub>, flows into the emitter of Q<sub>15</sub> and appears at its collector as I<sub>2</sub>, with opposite phase of I<sub>1</sub>, i.e. I<sub>2</sub> = -I<sub>1</sub>. To gain further insight on circuit operation, the simulated voltage and current waveforms are reported in Fig. 10c. The top, middle and bottom plot show the input voltages  $V_{in}^{\pm}$ , the voltages at the emitters of Q<sub>13,14</sub> and Q<sub>15</sub>, and the two output currents I<sub>1</sub>,I<sub>2</sub>. The tail bias current and the emitter area of Q<sub>15</sub> are the same as Q<sub>13,14</sub>. Therefore, at the quiescent point the emitter voltages V<sub>E1</sub>,V<sub>E2</sub>, are equal. But when the input signal is applied, the emitter voltage of Q<sub>13,14</sub>, V<sub>E1</sub>, follows the envelope and its mean value (DC component) is shifted upward proportionally to the amplitude of V<sub>in</sub>. This DC component is blocked by C<sub>4</sub> such that the mean value of  $V_{E2}$  remains the same as at the quiescent point, and thus  $V_{E1} > V_{E2}$  (middle plot in Fig. 10c). In this way, whatever it is the input signal amplitude,  $V_{BE-13,14} > V_{BE-15}$  near the peaks of  $|V_{in}|$  ( $\theta = \pi/2$  and  $\theta = 3/2\pi$  in Fig. 10c) while  $V_{BE-15} > V_{BE-13,14}$  near the zero crossings of  $V_{in}$  ( $\theta = 0$ ,  $\theta = \pi$  in Fig. 10c). Consequently, looking at the bottom plot in Fig. 10c,  $I_1 \sim I_{tail}$  and  $I_2 \sim 0$  near the peaks of  $V_{in}$  while  $I_2 \sim I_{tail}$  and  $I_1 = 0$  near the zero crossings of  $V_{in}$ .

With amplitude mismatch or phase deviation from 180° in  $V_{in}^{\pm}$ , a common-mode component at the input frequency drives the base terminals of the push-push transistors. For common mode, the simple push-push doubler in Fig. 10a behaves as a common-emitter stage, producing a large output signal leakage at the input frequency. In the proposed doubler the commonmode component on  $V_{in}^{\pm}$ , extracted by the RC network shown in Fig. 10b, feeds the base of Q15. Therefore, for a common-mode input signal Q<sub>13-14</sub> and Q<sub>15</sub> behave as a differential pair and do not transfer the common-mode input to the differential current I<sub>1</sub>-I<sub>2</sub>. To gain quantitative insight, Fig. 10d shows the simulated output current at twice the input frequency (I2f0) and the leakage of the fundamental frequency  $(I_{f0})$  with the simple push-push configuration of Fig. 10a and with the proposed doubler versus the input amplitude. The two circuits are designed with the same area of the input transistors and total bias current. 0.5dB amplitude imbalance and 5° phase error from 180° between  $V_{in}^+$ and  $V_{in}^-$  are assumed, leading to a leakage of I<sub>f0</sub> 19dB below I<sub>2f0</sub> in the simple push-push configuration. With the proposed frequency doubler the suppression of If0 is raised to 38dB. From Fig. 10d the magnitude of  $I_{2f0}$  in the proposed solution is reduced by 3.5dB. However, the penalty is less than the insertion loss of a typical passive filter that can exert the same

Fig. 12. Simulated amplitude and phase errors of the differential doubler output with and without  $L_{1,2}$ .

amount of harmonic rejection, not considering the area occupation. Moreover, the proposed solution offers a differential output which is often desirable in integrated transceivers.

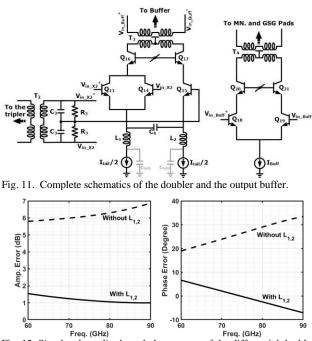

Fig. 11 shows the complete schematic of the frequency doubler and the output buffer. The input signal, generated by the tripler, is coupled with a transformer T<sub>2</sub> (260pH primary, 360pH secondary, with k=0.26) where at the secondary, C<sub>3</sub>=75fF senses the input common-mode and generates the base voltage of Q<sub>15</sub>. The DC bias voltage (1.1V) is applied through R<sub>3</sub>. Common-base transistors are stacked on Q<sub>13,14</sub> and Q<sub>15</sub> to mitigate the impact of miller capacitances. Q<sub>13,14</sub>, working in class C, have an emitter area of  $5x0.2\mu$ m<sup>2</sup>, and Q<sub>15-17</sub> have double that size. The differential output current feeds the primary winding of a transformer T<sub>3</sub>, used to couple the doubler to the output buffer and has an equivalent inductance of 100pH at its both primary and secondary with a coupling factor of 0.39.

The parasitic capacitances of the tail current sources,  $C_{tail1,2}$ , are around 70fF each, which is not negligible at the operating frequency. They appear in parallel to the signal path of the second harmonic current flowing from the emitter of  $Q_{13,14}$  to the emitter of  $Q_{15}$ , causing reduction of the conversion gain and amplitude and phase unbalance between the two output currents. Therefore, as shown in Fig. 11, two sufficiently large inductors (225pH),  $L_{1,2}$ , are placed in series with the current sources rising the impedance at the operating frequency and thus shielding the effect of  $C_{tail1,2}$ . Fig. 12 shows the simulated amplitude mismatch and phase deviation from 180° in the doubler output currents with and without  $L_{1,2}$ . Across the 60GHz to 90GHz output frequency range, the inductors reduce the amplitude mismatch from 6-7dB down to less than 1.5dB and the phase error from 20-35° down to  $\pm 7^{\circ}$ .

From simulations, the amplitude mismatch and phase deviation from  $180^{\circ}$  of the currents delivered by the doubler active core are within 1.5dB and +/-7°, respectively, across the 60GHz to 90GHz output frequency range.

The secondary of the transformer  $T_3$  drives the output buffer. The input transistors  $Q_{18,19}$  and the common-base transistors  $Q_{20,21}$  form a cascode differential amplifier. They all have the same emitter area of  $10x0.2\mu m^2$ . The transformer  $T_4$  and a passive network toward the output pad provide matching to a 50 $\Omega$  load and differential to single-ended conversion for measurements with a GSG probe.

#### VI. SEXTUPLER SIMULATIONS

The frequency sextupler comprises the cascade of the tripler and doubler with output buffer, as shown by the block diagram in Fig.1. Compared to the first version of the tripler, in the testchip described in Sec. IV [27], the tripler in the sextupler has been optimized to limit power consumption. In particular, the core supply voltage is reduced from 1.7V to 1.2V, as some voltage headroom was wasted in the first design, and the bias current is scaled down, from 13mA to 8mA, because the tripler's load to be driven in the sextupler chain is smaller than in the test-chip for the tripler alone. The doubler and output buffer following the tripler have been described in Sec. V.

From simulations with an input signal at  $f_0=12.5$ GHz, the

Table I. Simulation of HRR along the sextupler chain (within parentheses, in the second column, are reported calculated values)

| Tripler                                                                                  | Doubler output                       | Buffer                      |  |  |

|------------------------------------------------------------------------------------------|--------------------------------------|-----------------------------|--|--|

| output                                                                                   | (calculations in parentheses)        | output                      |  |  |

| $\frac{H_3}{2} = 46.5 dB$                                                                | $\frac{H_6}{H_3} = 40.7 dB \ (40.7)$ | $\frac{H_6}{H_3} = 53.1 dB$ |  |  |

| $\frac{\overline{H_1}}{\overline{H_1}} = 46.5 dB$ $\frac{H_3}{\overline{H_3}} = 58.9 dB$ | $\frac{H_6}{H_4} = 44.1dB \ (40.4)$  | $\frac{H_6}{H_4} = 49.5 dB$ |  |  |

| $\frac{\overline{H_2}}{H_3} = 59.3 dB$                                                   | $\frac{H_6}{H_5} = 52.5 dB \ (52.7)$ | $\frac{H_6}{H_5} = 60.8 dB$ |  |  |

| $H_4$<br>$H_3$ 40 dB                                                                     | $\frac{H_6}{H_7} = 55.1 dB \ (53)$   | $\frac{H_6}{H_7} = 67dB$    |  |  |

| $\overline{H_5} = 40 \ aB$                                                               | $\frac{H_6}{H_8} = 34.5 dB \ (33.9)$ | $\frac{H_6}{H_8} = 51.7 dB$ |  |  |

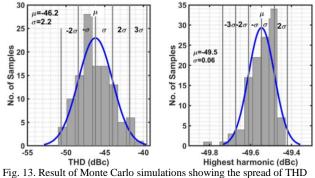

Fig. 13. Result of Monte Carlo simulations showing the spread of THL and the highest undesired harmonic.

saturated output power of the sextupler ate  $6f_0=75$ GHz, limited by the final buffer, is  $P_{out}=5.5$ dBm, with input power of -3dBm. This corresponds to a maximum conversion gain of 8.5dB. Simulations of the harmonic rejections along the chain are also performed and summarized in Table I. The first, second and third column report the HRR for different harmonics at the tripler, doubler and buffer output, with the desired output signal at  $6f_0=75$ GHz. Simulations are also compared with the polynomial modelling considered for the analysis in Sec. III. From the simulation results in the first column of Table I, the tripler output can be approximated as:

$$w \approx \frac{H_1}{H_3} \cos(\omega_0 t) + \frac{H_2}{H_3} \cos(2\omega_0 t) + \cos(3\omega_0 t) + \frac{H_4}{H_3} \cos(4\omega_0 t) + \frac{H_5}{H_3} \cos(5\omega_0 t)$$

(9)

with  $\omega_0=2\pi f_0$ .

The values within parentheses in the second column of Table I are calculated modeling the doubler with (1) if the input signal is given by (9). The parameter  $\rho$  in (1), determining the finite rejection of the fundamental component at the doubler output (which, for the doubler after the tripler, corresponds to  $3f_0$ ), is estimated from the simulated H<sub>6</sub>/H<sub>3</sub> of 40.7dB, leading to  $\rho$ =108. Calculations agree well with the simulated HRR, with only few dBs of error. Despite the approximations in the modeling approach introduced in Sec. III (neglecting e.g. higher order terms in the polynomial and memory effects), it still provides a good first order approximation of the unwanted harmonic levels.

Interestingly, considering even and odd harmonics at the tripler output and only a second-order polynomial model for the doubler, all the undesired output harmonics, up to the 8<sup>th</sup> are well predicted. As mentioned in footnote 1 in page 4, the  $7^{th}$  harmonic appears at the doubler output if the tripler output is not perfectly balanced and the doubler is fed by even harmonics (the  $4^{th}$  in particular).

Finally, to investigate the resiliency of the sextupler to process variation and mismatches, Monte Carlo simulations have been performed on the full chip. Fig.13 shows the results with a 0dBm input at 12.5GHz. The suppression of the largest unwanted harmonic and the total harmonic rejection at  $3\sigma$  are - 49.5dBc and -39.6dBc respectively.

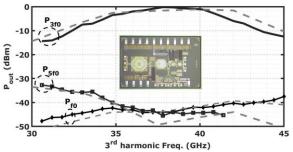

#### VII. MEASUREMENT RESULTS

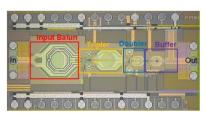

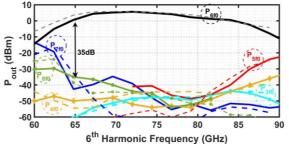

A photograph of the sextupler chip, fabricated in ST Microelectronics 55nm SiGe-BiCMOS technology, is shown in Fig. 14 and measures 810µm by 1440µm including all the signal and supply pads. The supply voltage for the tripler core is 1.2V, and for the ED, doubler and the buffer stage it is 1.7V. The current consumption of the tripler, ED, doubler and output buffer are 8mA, 0.6mA, 7.9mA, and 23mA, respectively. Fig. 15 shows the simulated and measured power delivered to a  $50\Omega$ load at 6f<sub>0</sub> and leakage of other harmonics of f<sub>0</sub> versus frequency when the sextupler is driven by a 0dBm input signal. The peak output power, Pout, is 5.6dBm at 72GHz corresponding to a power conversion efficiency,  $\eta =$  $P_{out}/(P_{DC} + P_{in}) = 5.6\%$ . The frequency component at  $6f_0$ remains above 0dBm from 64.7GHz to 84.7GHz, corresponding to a 26.8% BW, where the suppression of unwanted harmonics is better than 35dB. Moreover, Pout remains within 3dB variation from 65.9GHz to 78.6GHz. corresponding to 17.6% fractional BW. In this frequency range, the unwanted harmonics of the input are suppressed by more than 38.5dB. Consistent results are achieved by measurements repeated on different samples.

Overall, simulations and measurements in Fig. 15 are in good agreement. The largest discrepancy is on the 5<sup>th</sup> and 7<sup>th</sup> harmonics. As explained in Sec. VI, they arise from even harmonics at the output of tripler (nominally balanced) due to imbalances and asymmetries in the differential circuits and components (input balun, transformers) which are particularly difficult to be precisely modeled. The rapid increase of these harmonics at the edges of the band is expected also from simulations and it is attributed to the frequency response of the interstage band-pass networks (T<sub>2-4</sub> in Fig. 11). As an example, the simulated suppression of the 7<sup>th</sup> harmonic in Fig. 15 drops from 67dB when the input signal is at center frequency,  $f_0=12.5GHz$  (6 $f_0=75GHz$ ) to 15dB when f<sub>0</sub>=10GHz (6f<sub>0</sub>=60GHz). 7f<sub>0</sub> results from the beating of  $3f_0$  and the leakage of  $4f_0$  at the tripler output. With  $f_0$  reduced to 10GHz, the desired signal at  $3f_0$  moves below the passband of  $T_2$  while  $4f_0$ moves closer to its center frequency. As a result, H<sub>3</sub>/H<sub>4</sub> ratio is reduced (by ~20dB). Following the analysis of Sec. III, it can be shown that this in turn results in the same reduction of  $H_6/H_7$ at the doubler output. After the doubler,  $6f_0$  moves below the passband of T<sub>3</sub> and T<sub>4</sub> while 7f<sub>0</sub> is more close to the center frequency, hence the  $H_6/H_7$  ratio degrades (~15dB through T<sub>3</sub> and  $\sim$ 15dB though the buffer and T<sub>4</sub>). Therefore, it is expected

9

Fig. 14. Chip photograph of the frequency sextupler.

Fig. 15. Measured (solid) and simulated (dashed) output power of the 6<sup>th</sup> harmonic and of undesired harmonics versus frequency for 0dBm input signal.

Fig. 16. Measured (solid) and simulated (dashed) output power of the 6<sup>rd</sup> harmonic ( $P_{6fo}$ ) and all the unwanted harmonics ( $P_{Spurs}$ ) at  $f_0=12.4$ GHz.

Fig. 17. Measured input and output phase noise.

that  $H_6/H_7$  reduces by around 50dB. Nevertheless, in the bandwidth of interest, all unwanted harmonics, including the 5<sup>th</sup> and 7<sup>th</sup>, are heavily suppressed.

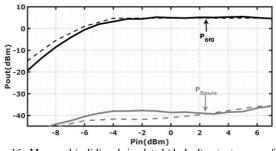

Fig. 16 shows the simulated and measured output power at  $6f_0$  when the input power is swept at 12.4GHz. The same plot reports the total power of unwanted harmonics. The output saturates when the input power reaches -3dBm, and from - 3dBm to 7 dBm, the variation of the output power is within 1dB. The total HRR is better than 40dB for input power larger than - 5.5dBm.

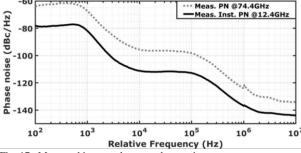

Fig. 17 shows the phase noise at the input and output of the sextupler when the output frequency is 74.4GHz. The difference between the two plots is 15.5dB, as expected by the frequency multiplication by 6, proving negligible phase noise

| Ref       | Tech        | ×N | fout (GHz)          | Supp. of<br>Harm. (dB) | P <sub>out</sub><br>(dBm) | Conv.<br>Gain (dB) | $P_{DC}(mW)$ | η (%) |

|-----------|-------------|----|---------------------|------------------------|---------------------------|--------------------|--------------|-------|

| [17]      | 65nm CMOS   | 9  | 88-99.5 (12.2%)     | 31                     | 8.5                       | -5.7               | 438          | 1.5   |

| [45]      | 65nm CMOS   | 9  | 88.9-95.5 (7.2%)    | 16                     | -1.8                      | 1.4                | 120          | 0.55  |

| [46]      | 100nm pHEMT | 8  | 90.5-95.2 (5%)      | 21                     | -0.4                      | -0.6               | 138          | 0.65  |

| [47]      | 65nm CMOS   | 8  | 84-98.4 (15.3%)     | 10                     | -7.12                     | -7.12              | 1            | 9.7   |

| [48]      | 90nm CMOS   | 6  | 96.1-98.4 (2.3%)    | NA                     | -17.2                     | -17.2              | 55.4         | 0.04  |

| [49]      | 100nm HEMT  | 6  | 155-195 (22.8%)     | 20                     | 0                         | -6.5               | 92.5         | 1     |

| [50]      | 65nm CMOS   | 6  | 74.7-82.2 (9.6%)    | NA                     | 4                         | 4                  | 51           | 4.8   |

| [16]      | 100nm HEMT  | 6  | 78-104 (28.6%)      | 25                     | 7                         | 5                  | 470          | 1     |

| [51]      | SiGe BiCMOS | 4  | 70-110 (44.5%)      | 30                     | 3                         | 3                  | 170          | 1.17  |

| [52]      | SiGe BiCMOS | 4  | 62-76 (20%)         | 33                     | 9                         | NA                 | 262          | ~3    |

| [53]      | SiGe BiCMOS | 4  | 99-132 (28.6%)      | 25                     | 8.5                       | 8.5                | 79           | 8.8   |

| [54]      | SiGe BiCMOS | 3  | 69-86 (22%)         | 33                     | 9.9                       | 7.9                | 158          | 6.12  |

| [32]      | SiGe BiCMOS | 3  | 80-100 (20%)        | 20                     | -10.5                     | -10.5              | 75           | 0.12  |

| [36]      | SiGe BiCMOS | 3  | 48-58 (19%)         | 28                     | 9.5                       | 12                 | 220          | 4     |

| [55]      | 0.15um HEMT | 3  | 58.5-65 (10.5%)     | 19                     | -0.4                      | -4.4               | 52           | 1.67  |

| [56]      | 65nm CMOS   | 3  | 57-78 (31%)         | 20                     | -3.7                      | 1.3                | 60           | 0.7   |

| This work | SiGe BiCMOS | 6  | 65.9-78.6 (17.6%)*  | >38.5                  | 5.6                       | 5.6***             | 63.1         | 5.66  |

| This work | SiGe BiCMOS | 6  | 64.7-84.7 (26.8%)** | >35                    | 5.6                       | 5.6***             | 63.1         | 5.66  |

Table II. Measurement summary and comparison of the sextupler chip with other frequency multipliers in the same frequency range.

\*-3dB BW \*\*>0dBm

\*\*\* at center frequency, with 0dBm input power. The maximum conversion gain is 8.5dB with Pin=-3dBm

deterioration from the sextupler chain.

Finally, measurement results are summarized in Table II and compared against previously reported frequency multipliers with similar output frequency. The presented frequency sextupler achieves bandwidth and output power aligned with state of the art, but with excellent power efficiency and the highest suppression of undesired harmonics of at least 35dB. Among other works, the highest reported suppression is around 30dB, achieved by the quadruplers in [51, 52] and the multiplier by 9 in [17] with 3x or more higher power consumption and lower power efficiency, and by a tripler alone in [54]. Also the quadrupler in [53] has a remarkable efficiency while maintaining high output power and bandwidth, but a simulated harmonic suppression of only 25dB.

#### VIII. CONCLUSION

A frequency sextupler with novel tripler and doubler circuit topologies featuring enhanced suppression of unwanted harmonics has been presented. The tripler core is devised to reproduce the trans-characteristic of a 3<sup>rd</sup> order polynomial that ideally generates only the 3<sup>rd</sup> harmonic of a sinusoidal input signal. The operation is robust against variation of the input signal power thanks to an adaptive biasing circuit implemented with an envelope detector. The frequency doubler is an evolution of the push-push topology modified to produce a

differential output current and to improve the robustness against amplitude and phase unbalances of the driving signals, thus improving substantially the rejection of the fundamental frequency component. Implemented in a 55nm SiGe-BiCMOS technology with 63.1mW total power dissipation, the sextupler circuit achieves bandwidth and output power aligned with state of the art, but with excellent rejection of undesired harmonic components and power efficiency.

#### REFERENCES

- T. S. Rappaport *et al.*, "Millimeter Wave Mobile Communications for 5G Cellular: It Will Work!," *IEEE Access*, vol. 1, pp. 335-349, 2013.

- [2] L. Gomes et al., "77.3-GHz Standing-Wave Oscillator Based on an Asymmetrical Tunable Slow-Wave Coplanar Stripline Resonator," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 68, no. 8, pp. 3158-3169, 2021.

- [3] A. Basaligheh, P. Saffari, I. M. Filanovsky, and K. Moez, "A 65–81 GHz CMOS Dual-Mode VCO Using High Quality Factor Transformer-Based Inductors," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 67, no. 12, pp. 4533-4543, 2020.

- [4] E. Sharma et al., "Design of a 77-GHz LC-VCO With a Slow-Wave Coplanar Stripline-Based Inductor," *IEEE Transactions on Circuits* and Systems I: Regular Papers, vol. 67, no. 2, pp. 378-388, 2020.

- [5] R. Kananizadeh and O. Momeni, "A 190-GHz VCO With 20.7% Tuning Range Employing an Active Mode Switching Block in a 130 nm SiGe BiCMOS," *IEEE Journal of Solid-State Circuits*, vol. 52, no. 8, pp. 2094-2104, 2017.

- [6] K. Wu and M. Hella, "A 103-GHz Voltage Controlled Oscillator with 28% Tuning Range and 4.2 dBm Peak Output Power Using

SiGe BiCMOS Technology," in *IEEE/MTT-S International Microwave Symposium - IMS*, 10-15 June 2018, pp. 606-609.

- [7] A. Mostajeran and E. Afshari, "An ultra-wideband harmonic radiator with a tuning range of 62GHz (28.3%) at 220GHz," in *IEEE Radio Frequency Integrated Circuits Symposium (RFIC)*, 4-6 June 2017, pp. 164-167.

- [8] Z. Zong and R. B. Staszewski, "Effects of Subharmonics in LO Generation on RF Transceivers," in *IEEE MTT-S International Microwave Workshop Series on 5G Hardware and System Technologies (IMWS-5G)*, 30-31 Aug. 2018, pp. 1-3.

- [9] S. Yoo, S. Choi, J. Kim, H. Yoon, Y. Lee, and J. Choi, "A Low-Integrated-Phase-Noise 27–30-GHz Injection-Locked Frequency Multiplier With an Ultra-Low-Power Frequency-Tracking Loop for mm-Wave-Band 5G Transceivers," *IEEE Journal of Solid-State Circuits*, vol. 53, no. 2, pp. 375-388, Feb. 2018.

- [10] S. Kim, C. Choi, C. Cui, B. Kim, and M. Seo, "A W-Band Signal Generation Using N-Push Frequency Multipliers for Low Phase Noise," *IEEE Microwave and Wireless Components Letters*, vol. 24, no. 10, pp. 710-712, Oct 2014.

- [11] W. L. Chan and J. R. Long, "A 56–65 GHz Injection-Locked Frequency Tripler With Quadrature Outputs in 90-nm CMOS," *IEEE Journal of Solid-State Circuits*, vol. 43, no. 12, pp. 2739-2746, Dec. 2008.

- [12] W. Lee, T. Dinc, and A. Valdes-Garcia, "Reconfigurable 60-GHz Radar Transmitter SoC with Broadband Frequency Tripler in 45nm SOI CMOS," in *IEEE Radio Frequency Integrated Circuits Symposium (RFIC)*, Boston, MA, USA, 2-4 June 2019, pp. 43-46.

- [13] Z. Chen, Y. Wu, Y. Yu, C. Zhao, H. Liu, and K. Kang, "A K-Band Frequency Tripler Using Transformer-Based Self-Mixing Topology With Peaking Inductor," *IEEE Transactions on Microwave Theory* and Techniques, vol. 68, no. 5, pp. 1688-1696, 2020.

- [14] M. Ko, M. H. Eissa, J. Borngräber, A. C. Ulusoy, and D. Kissinger, "110–135 GHz SiGe BiCMOS Frequency Quadrupler Based on a Single Gilbert Cell," in 13th European Microwave Integrated Circuits Conference (EuMIC), 23-25 Sept. 2018, pp. 101-104.

- [15] M. Bassi et al., "A 39-GHz Frequency Tripler With >40-dBc Harmonic Rejection for 5G Communication Systems in 28-nm Bulk CMOS," in *IEEE 45th European Solid State Circuits Conference* (ESSCIRC), Cracow, Poland, 23-26 Sept. 2019, pp. 107-110.

- [16] I. Kallfass et al., "A W-band active frequency-multiplier-by-six in waveguide package," in German Microwave Conference Digest of Papers, Berlin, Germany, 15-17 March 2010, pp. 74-77.

- [17] N. Mazor and E. Socher, "Analysis and design of an X-band-to-Wband CMOS active multiplier with improved harmonic rejection," *IEEE Transactions on Microwave Theory and Techniques*, vol. 61, no. 5, pp. 1924-1933, May 2013.

- [18] X. Liu and H. C. Luong, "A 170-GHz 23.7% Tuning-Range CMOS Injection-Locked LO Generator With Third-Harmonic Enhancement," *IEEE Transactions on Microwave Theory and Techniques*, vol. 68, no. 7, pp. 2668-2678, 2020.

- [19] N. Mazor et al., "A SiGe V-band x8 frequency multiplier with high spectral purity," in 10th European Microwave Integrated Circuits Conference (EuMIC), Paris, France, 7-8 Sept. 2015, pp. 77-80.

- [20] A. Ali, J. Yun, M. Kucharski, H. J. Ng, D. Kissinger, and P. Colantonio, "220–360-GHz Broadband Frequency Multiplier Chains (x8) in 130-nm BiCMOS Technology," *IEEE Transactions on Microwave Theory and Techniques*, vol. 68, no. 7, pp. 2701-2715, 2020.

- [21] J. Song, C. Cui, S. Kim, B. Kim, and S. Nam, "A Low-Phase-Noise 77-GHz FMCW Radar Transmitter With a 12.8-GHz PLL and a X6 Frequency Multiplier," *IEEE Microwave and Wireless Components Letters*, vol. 26, no. 7, pp. 540-542, July 2016.

- [22] D. Liao, Y. Zhang, F. F. Dai, Z. Chen, and Y. Wang, "An mm-Wave Synthesizer With Robust Locking Reference-Sampling PLL and Wide-Range Injection-Locked VCO," *IEEE Journal of Solid-State Circuits*, vol. 55, no. 3, pp. 536-546, 2020.

- [23] J. Zhang, Y. Peng, H. Liu, Y. Wu, C. Zhao, and K. Kang, "A 21.7to-41.7-GHz Injection-Locked LO Generation With a Narrowband Low-Frequency Input for Multiband 5G Communications," *IEEE Transactions on Microwave Theory and Techniques*, vol. 68, no. 1, pp. 170-183, 2020.

- [24] X. Liu and H. C. Luong, "A Fully Integrated 0.27-THz Injection-Locked Frequency Synthesizer With Frequency-Tracking Loop in 65-nm CMOS," *IEEE Journal of Solid-State Circuits*, vol. 55, no. 4, pp. 1051-1063, 2020.

- X. Liu, Y. Chao, and H. C. Luong, "A 59-to-276-GHz CMOS Signal Generator Using Varactor-Less VCO and Dual-Mode ILFD," *IEEE Journal of Solid-State Circuits*, vol. 56, no. 8, pp. 2324-2334, 2021.

"D-band RAdio 5G netwOrk techNology (DRAGON)." [Online].

- Available: <u>https://www.h2020-dragon.eu/</u>

[27] M. M. Pirbazari, F. Pepe, and A. Mazzanti, "40GHz Frequency Tripler with High Eurodemental and Harmonics Pajection in 55mm

- Tripler with High Fundamental and Harmonics Rejection in 55nm SiGe-BiCMOS," in *ESSCIRC 2019 IEEE 45th European Solid State Circuits Conference*, 23-26 Sept. 2019, pp. 229-232.

Y. Ye, B. Yu, A. Tang, B. Drouin, and Q. J. Gu, "A High Efficiency

- [28] Y. Ye, B. Yu, A. Tang, B. Drouin, and Q. J. Gu, "A High Efficiency E-Band CMOS Frequency Doubler With a Compensated Transformer-Based Balun for Matching Enhancement," *IEEE Microwave and Wireless Components Letters*, vol. 26, no. 1, pp. 40-42, 2016.

- [29] H. Lin and G. M. Rebeiz, "A 135–160 GHz balanced frequency doubler in 45 nm CMOS with 3.5 dBm peak power," in *IEEE MTT-S International Microwave Symposium (IMS2014)*, 1-6 June 2014, pp. 1-4.

- [30] I. Lee, Y. Kim, and S. Jeon, "108–316- and 220–290-GHz Ultrabroadband Distributed Frequency Doublers," *IEEE Transactions on Microwave Theory and Techniques*, vol. 68, no. 3, pp. 1000-1011, 2020.

- [31] S. Carpenter, Z. S. He, V. Vassilev, and H. Zirath, "A +14.2 dBm, 90–140 GHz Wideband Frequency Tripler in 250-nm InP DHBT Technology," *IEEE Microwave and Wireless Components Letters*, vol. 28, no. 3, pp. 239-241, March 2018.

- [32] C. Wang, Z. Chen, and P. Heydari, "W-Band Silicon-Based Frequency Synthesizers Using Injection-Locked and Harmonic Triplers," *IEEE Transactions on Microwave Theory and Techniques*, vol. 60, no. 5, pp. 1307-1320, May 2012.

- [33] M. Chou, H. Chiu, H. Kao, and F. Huang, "A 60-GHz CMOS Frequency Tripler With Broadband Performance," *IEEE Microwave* and Wireless Components Letters, vol. 27, no. 3, pp. 281-283, March 2017.

- [34] Z. Chen and P. Heydari, "An 85-95.2 GHz transformer-based injection-locked frequency tripler in 65nm CMOS," in *IEEE MTT-S International Microwave Symposium*, Anaheim, CA, USA, 23-28 May 2010, pp. 776-779.

- [35] L. Iotti, G. LaCaille, and A. M. Niknejad, "A 57–74-GHz Tail-Switching Injection-Locked Frequency Tripler in 28-nm CMOS," in *IEEE 45th European Solid State Circuits Conference (ESSCIRC)*, Cracow, Poland, 23-26 Sept. 2019, pp. 115-118.

- [36] N. Mazor et al., "A high suppression frequency tripler for 60-GHz transceivers," in *IEEE MTT-S International Microwave Symposium*, Phoenix, AZ, USA, 17-22 May 2015, pp. 1-4.

- [37] S. Li, T. Chi, T.-Y. Huang, M.-Y. Huang, D. Jung, and H. Wang, "A buffer-less wideband frequency doubler in 45-nm CMOS-SOI with transistor multiport waveform shaping achieving 25% drain efficiency and 46–89 GHz instantaneous bandwidth," *IEEE Solid-State Circuits Letters*, vol. 2, no. 4, pp. 25-28, April 2019.

- [38] G. Liu, J. Jayamon, J. Buckwalter, and P. Asbeck, "Frequency doublers with 10.2/5.2 dBm peak power at 100/202 GHz in 45nm SOI CMOS," in *IEEE Radio Frequency Integrated Circuits Symposium (RFIC)*, 17-19 May 2015, pp. 271-274.

- [39] L. Vera and J. R. Long, "A DC-100 GHz Active Frequency Doubler With a Low-Voltage Multiplier Core," *IEEE Journal of Solid-State Circuits*, vol. 50, no. 9, pp. 1963-1973, 2015.

- [40] S. Chakraborty, L. E. Milner, S. Mahon, A. Parker, and M. Heimlich, "A GaAs Frequency Doubler with 38 dB fundamental rejection from 22 to 40 GHz using a Transformer Balun," in 14th European Microwave Integrated Circuits Conference (EuMIC), Paris, France, 30 Sept.-1 Oct. 2019, pp. 294-297.

- [41] A. Mazzanti and A. Bevilacqua, "Second-Order Equivalent Circuits for the Design of Doubly-Tuned Transformer Matching Networks," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 65, no. 12, pp. 4157-4168, 2018.

- [42] A. Bevilacqua and A. Mazzanti, "Doubly-Tuned Transformer Networks: A Tutorial," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 68, no. 2, pp. 550-555, 2021.

- [43] S. Chakraborty, L. E. Milner, X. Zhu, L. T. Hall, O. Sevimli, and M. C. Heimlich, "A K-Band Frequency Doubler With 35-dB Fundamental Rejection Based on Novel Transformer Balun in 0.13-um SiGe Technology," *IEEE Electron Device Letters*, vol. 37, no. 11, pp. 1375-1378, Nov. 2016.

- [44] K. Wu, S. Muralidharan, and M. M. Hella, "A Wideband SiGe BiCMOS Frequency Doubler With 6.5-dBm Peak Output Power for Millimeter-Wave Signal Sources," *IEEE Transactions on Microwave Theory and Techniques*, vol. 66, no. 1, pp. 187-200, Jan. 2018.

- [45] N. Mazor and E. Socher, "X-Band to W-Band Frequency Multiplier in 65 nm CMOS Process," *IEEE Microwave and Wireless Components Letters*, vol. 22, no. 8, pp. 424-426, Aug. 2012.

- [46] K. Park, D. Kim, I. Lee, and S. Jeon, "W -Band Injection-Locked Frequency Octupler Using a Push–Push Output Structure," *IEEE Microwave and Wireless Components Letters*, vol. 29, no. 12, pp. 822-825, 2019.

- [47] W. Chung, C. Kim, S. S. Kim, and S. Hong, "Design of 94-GHz Highly Efficient Frequency Octupler Using 47-GHz Current-Reusing Class-C Frequency Quadrupler," *IEEE Transactions on Microwave Theory and Techniques*, vol. 68, no. 2, pp. 775-784, 2020.

- [48] Y. Yen-Liang, H. Chih-Sheng, and C. Hong-Yeh, "A 20.7% locking range W-band fully integrated injection-locked oscillator using 90 nm CMOS technology," in 2012 IEEE/MTT-S International Microwave Symposium Digest, Montreal, QC, Canada, 17-22 June 2012, pp. 1-3.

- [49] M. Abbasi et al., "Single-Chip Frequency Multiplier Chains for Millimeter-Wave Signal Generation," *IEEE Transactions on Microwave Theory and Techniques*, vol. 57, no. 12, pp. 3134-3142, Dec. 2009.

- [50] Y. Chang, Y. Hsiao, Y. Lin, and H. Wang, "A W-band LO-chain with injection-locked frequency sextupler and medium power amplifier using 65-nm CMOS technology for automotive radar applications," in 2015 Asia-Pacific Microwave Conference (APMC), Nanjing, China, 6-9 Dec. 2015, vol. 1, pp. 1-3.

- [51] B. Ku, H. Chung, and G. M. Rebeiz, "A Milliwatt-Level 70–110 GHz Frequency Quadrupler With >30 dBc Harmonic Rejection," *IEEE Transactions on Microwave Theory and Techniques*, vol. 68, no. 5, pp. 1697-1705, 2020.

- [52] R. Levinger *et al.*, "High-Performance E-Band Transceiver Chipset for Point-to-Point Communication in SiGe BiCMOS Technology," *IEEE Transactions on Microwave Theory and Techniques*, vol. 64, no. 4, pp. 1078-1087, 2016.

- [53] K. Wu, M. W. Mansha, and M. Hella, "A 99 132 GHz Frequency Quadrupler with 8.5 dBm Peak Output Power and 8.8% DC-to-RF Efficiency in 130 nm BiCMOS," in *IEEE/MTT-S International Microwave Symposium (IMS)*, 4-6 Aug. 2020, pp. 476-479.

- [54] P. Zhou *et al.*, "A High-Efficiency E-band SiGe HBT Frequency Tripler with Broadband Performance," in *IEEE/MTT-S International Microwave Symposium - IMS*, 10-15 June 2018, pp. 690-693.

- [55] N. Kuo, J. Kao, Z. Tsai, K. Lin, and H. Wang, "A 60-GHz Frequency Tripler With Gain and Dynamic-Range Enhancement," *IEEE Transactions on Microwave Theory and Techniques*, vol. 59, no. 3, pp. 660-671, March 2011.

- [56] Y. Lee, Y. Hsiao, and H. Wang, "A 57–78 GHz Frequency Tripler MMIC in 65-nm CMOS," *IEEE Microwave and Wireless Components Letters*, vol. 26, no. 9, pp. 723-725, 2016.

**Mahmoud M. Pirbazari** (S'17–M'21) received his M.Sc. Degree in Electrical Engineering from Urmia University,

Urmia, Iran, and his Ph.D. degree in microelectronics from the University of Pavia, Pavia, Italy, in 2014 and 2020, respectively.

He joined the AIC Lab at the University of Pavia in 2017 as a researcher where he started his Ph.D. in the same year. The main focus of his Ph.D. research activity was on frequency multiplication circuits with outputs at E- to D-band used in high data rate millimeter-

wave transceivers for which he received the 2020 SSCS Pre-Doctoral achievements' award. He is currently with the AIC Lab as a postdoctoral researcher working on millimeter-wave circuit building blocks in BiCMOS technology.

Andrea Mazzanti (S'02-M'09-SM'13) received the Laurea and Ph.D. degrees in electrical engineering from the University of Modena and Reggio Emilia, Modena, Italy, in 2001 and 2005, respectively. During the summer of 2003, he was with Agere Systems, Allentown, PA as an Intern. From

2006 to 2009, he was Assistant Professor with the University of Modena and Reggio Emilia. In January 2010, he joined the University di Pavia where he is now Full Professor. He has authored over 100 technical papers. His main research interests cover device modeling and IC design for high-speed communications, RF and millimeter-wave systems. Dr. Mazzanti has been a member of the Technical Program Committee of the IEEE Custom Integrated Circuit Conference (CICC) from 2008 to 2014, IEEE European Solid State Circuits Conference (ESSCIRC) and IEEE International Solid State Circuits Conference (ISSCC) from 2014 to 2018. He has been Associate Editor for the Transactions on Circuits and Systems-I from 2012 to 2015 and Guest Editor for special issues of the Journal of Solid State Circuits dedicated to CICC 2013-14 and ESSCIRC-2015. Since 2017, he has been serving as an Associate Editor for the IEEE Solid-State Circuits Letters .